PIC32MM CPU僔僗僥儉

椷榓 2擭 5寧15擔

丂UARTx2偺巇條傪尒捈偟傑偡乮俀乯

丂懠偺帠偵婥傪偲傜傟偰倀倎倰倲x2婎斅偺昡壙偑僲價僲價偵側偭偰偟傑偄傑偟偨丅

婎斅偼悘暘偲慜偵摓拝偟偰幚憰丒弶婜昡壙傑偱偼廔傢偭偰偄偨偺偱偡偑丄偦偙偱曻抲忬懺偵側偭偰偄傑偟偨丅

廬棃偺婎斅偲怴婯婎斅偺奜娤傪壓婰偵帵偟傑偡丅

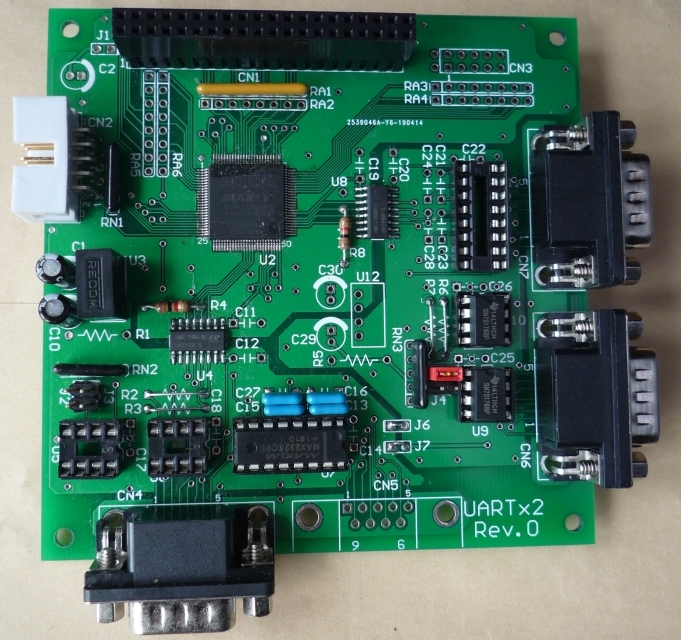

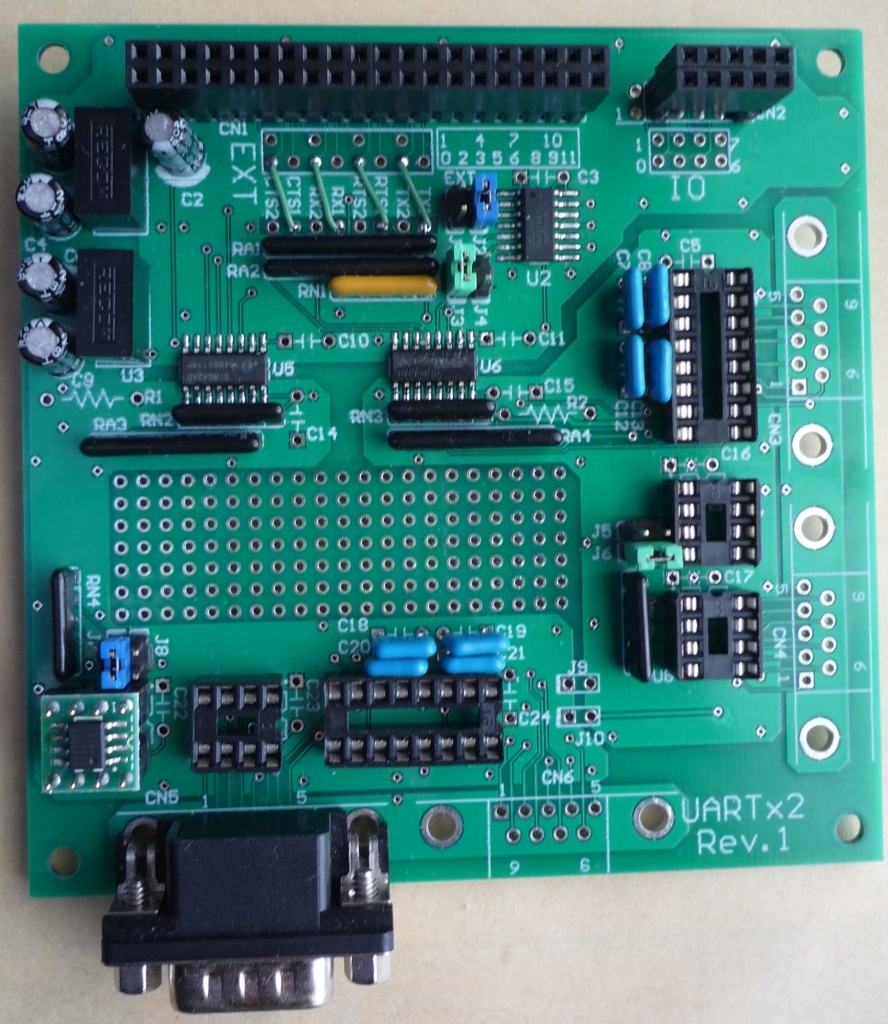

丂丂丂丂丂丂恾(a) Rev0(媽婎斅) 丂丂丂丂丂丂丂丂丂丂丂丂丂丂丂恾(b) Rev1(怴婎斅)

怴婯斉偺傎偆偼摦嶌専徹拞偺幨恀偺偨傔丄曅曽偺俠俫偺傒僐僱僋僞傪幚憰偟偰偄傑偡丅

偙偺幨恀偱偼俼俽-485偺摦嶌傪専徹偟偰偄傞帪偺幨恀偱丄僪儔僀僶IC偲偟偰SOIC僷僢働乕僕偺俬俠傪

俢俬俹偵曄姺偟偨傕偺傪幚憰偟偰偄傑偡丅

丂怴媽偺婎斅偱戝偒偔堎側傞偺偼婎斅偺拞墰晅嬤偵偁偭偨俠俹俴俢偑柍偔側偭偰偄傞偙偲偱偡丅

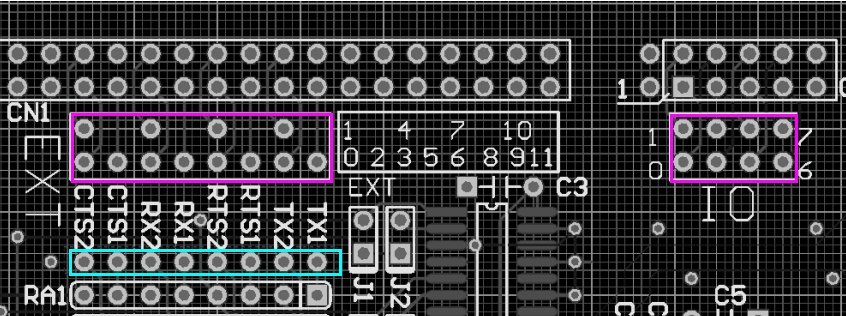

CPLD偱幚峴偟偰偄偨UART偺奺怣崋傪奼挘僐僱僋僞偺奺怣崋慄偵愙懕偡傞張棟偼僕儍儞僷慄偱戙梡偝傟偰偄傑偡丅

幨恀偱偼拞墰晹偺傗傗忋懁偵4杮偺僕儍儞僷慄偑尒偊偰偄傑偡丅

偙偺僕儍儞僷慄偺晅嬤傪CAD偱奼戝偟偨偺偑壓偺恾偱丄奺UART偺怣崋慄傪奼挘僐僱僋僞偺怣崋慄偵愙懕偡傞

條巕偑暘偐傝傑偡丅

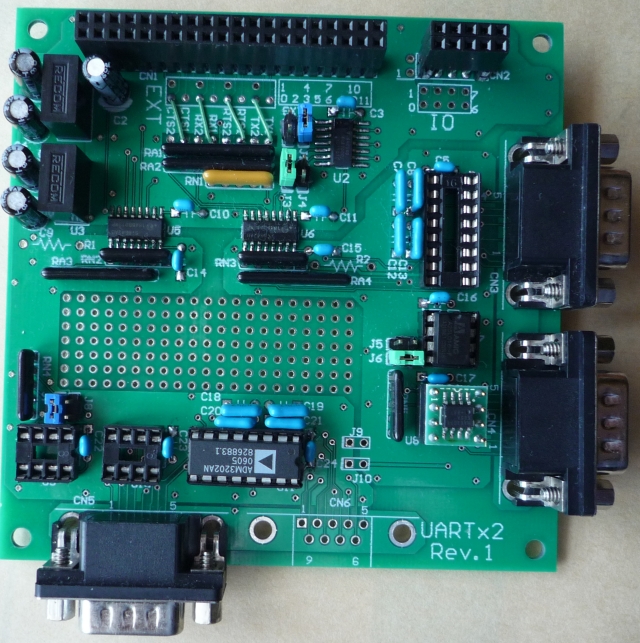

RS-232C, RS-422, RS-485偺奺俬俥偱偺摦嶌妋擣偑弌棃偨偺偱丄巆傝偺1CH偵偮偄偰傕摨條偺専徹傪峴側偄傑偟偨丅

惢昳偺幚憰僒儞僾儖偲偟偰RS-232C, RS-422峔惉偺幨恀傪帵偟傑偡丅

幨恀偱偼暘偐傝偯傜偄偱偡偑丄CH2暘偺僕儍儞僷乕攝慄偼棤柺偱攝慄偟偰偁傝傑偡丅

傑偨丄幨恀偱偼RS-422偺庴怣IC偲偟偰SOIC僷僢働乕僕傪巊梡偟偰偄傑偡偑丄惢昳偺擖庤偑娫偵崌偊偽DIP僷僢働乕僕偵

曄峏偟傑偡丅

PIC32MM栚師傊 丂慜傊 丂師傊